人体和电子设备等带电物体接触,会产生静电放电。将这个现象称为「ESD:Electro-Static Discharge」。人体产生的ESD是数千V的高电压,这个高电压脉冲侵入到触摸的电子设备内部,引起IC电路的误操作和IC电路破坏。为了防止像这样侵入电子设备内部的ESD对产品和系统产生破坏,有必要安装抑制和去除ESD的对策元件。

静电产生的原因

自然界中的所有物质都是由称为分子的粒子组成的,并且是电中性的,而分子是由一个或多个带有正电荷质子、负电荷电子和不带电荷中子的原子组成的。在正常情况下,质子的数量将与电子的数量相同,所以物体将是电中性的,也就是说,它们将在外部不带电荷。当一种物质受到外部能量的影响时,例如两个不同材料的物体之间的接触摩擦,其中一个物体将失去电子并带正电,而另一个物体将获得相同数量的电子并带负电,这根据其材料、粗糙表面和温度等各种属性或参数而变化。如果电荷在分离过程中难以中和,电荷将会积累并使物体带静电。

除了摩擦起电,感应起电是给物体充电的另一种方式。当一个带电物体接近一个不带电的金属球时,金属球会被感应吸引。此时,金属球将接地,电子将从金属球流向地面或(从地面注入金属球),然后地面将被移除,金属球将带正电或负电。当这些带电物体与导体接触时,它们往往是电中性的,这导致电流的产生。这些现象可能导致数千伏电压,并损坏我们日常使用的电子产品。

静电防护的重要性

1947年,John Bardeen和Walter Brattain在贝尔实验室发现,当两个金属点加到锗晶体上时,输出端的信号功率将大于输入端的信号功率。世界上第一个晶体管就这样制造出来了。到了西元1959年,他们首先在贝尔实验室发明了金属氧化物半导体场效应晶体管。到目前为止,锗已经在很大程度上被硅所取代,硅已经成为半导体工业的基石。

根据Gordon Moore的观察,集成电路上的晶体管数量每十八个月翻一番,这就是众所周知的摩尔定律。缩小晶体管尺寸的优点是在相同的布局面积下可以允许更复杂的电路;或功能相同但布局面积较小的电路,从而达到降低成本的效果。为了提高集成度和降低单位成本,互补金属氧化物半导体场效应晶体管的器件尺寸越来越小,但随之而来的是可靠性问题。晶体管小型化的项目之一是使栅极电介质层越来越薄。众所周知,栅极电介质层通常由二氧化硅制成,其可以承受大约10 MV/cm的电场强度。因此,当栅极电介质层的尺寸较小时,它能够承受的击穿电压变得越来越小,并且它更容易受到静电放电的影响,并且增加了故障的可能性。如今,电子产品的功能越来越多,相应的输入/输出端口(I/O端口)也越来越多,这使得静电更容易干扰或损坏集成电路。静电放电导致的产品失效问题对制造成本、产品质量和可靠性以及企业利润的影响越来越大,这也是静电防护问题越来越受到重视的原因。静电防护对当今的电子设备具有重要意义。

ESD防护的基本概念

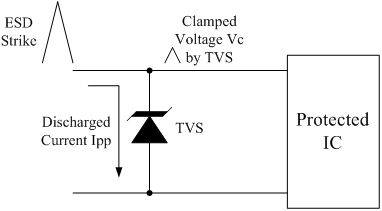

ESD保护电路专门用于保护集成电路。ESD保护电路可提供静电放电路径,以避免ESD期间静电电流流入集成电路所造成的损坏。在正常工作条件下,ESD保护电路将呈现高阻抗状态,因此电流可以正常流入内部电路。尽管仍会有少量漏电流流过ESD保护电路,但理想情况下,我们可以将此时的ESD保护电路视为开路。当出现异常高电压时,ESD保护电路将快速开启,为ESD电流提供低阻抗路径,从而避免大的ESD电流流入内部电路造成的损坏。此外,ESD保护电路会在一定的时间间隔内钳制过高的电压,以避免电路中的元件无法承受高电压而导致崩溃。

如何选择ESD防护电路

VDD为电源电压(power supply voltage)、Vh为维持电压(holding voltage)、Vt1为触发电压(trigger voltage)、VBD为击穿电压(gate oxide breakdown voltage)。ESD保护电路的设计窗口必须在蓝色虚线内。首先,维持电压是箝位电压的最小值,它必须大于VDD。否则,这种保护电路特性将使集成电路在实际系统应用中受到阻碍。其次,在正常系统运行下,维持保护电路可能会被误触发。触发电压是开启ESD保护电路所需的最小电压,必须小于VBD,否则ESD保护电路不会开启,集成电路内部元件的栅极氧化层会被这个大电压损坏。Ron是ESD保护电路的导通电阻,导通电阻越小越好。这样,当静电放电发生时,箝位电压变小,产生的热量变小,从而避免了ESD保护电路的损坏。