一、主要失效原因分类

1. 外部应力损伤

(1)静电放电(ESD)击穿

成因:MOSFET栅源极(G-S)间电容极小(几pF),输入阻抗极高(10⁹Ω+),少量静电电荷(如人体、环境摩擦产生)通过公式 U=Q/C 可生成数百伏高压,直接击穿G-S绝缘层。

典型场景:未接地的操作环境、化纤衣物摩擦、干燥环境下的器件搬运。

预防措施:存储和运输时使用金属容器或导电材料包装,避免接触易产生静电的材料;操作时确保工具、仪表和工作台接地,操作人员应穿棉质衣物并佩戴防静电手环。

(2)过流、过压、过温

成因:

过流:输入端保护二极管电流容限仅约1mA,瞬态电流超过10mA(如浪涌、负载突变)时,二极管过热烧毁,失去保护作用。

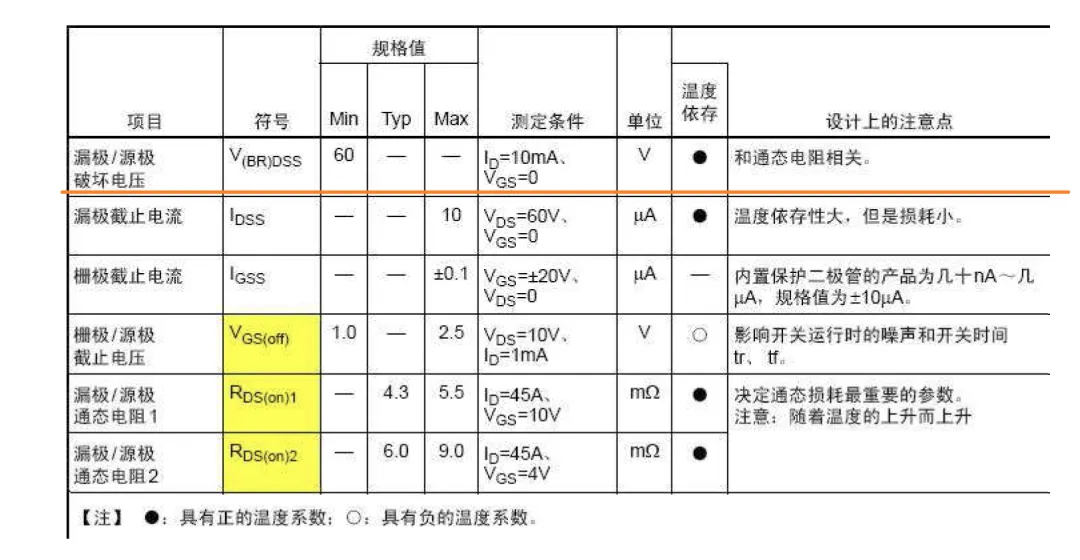

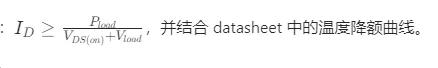

过压:栅极电压超过额定值(如驱动电路故障),导致氧化层击穿;漏源极(D-S)间电压超过耐压值(VDS),引发雪崩击穿。

预防措施:选择耐压值高于电路最大工作电压1.5倍的器件,感性负载并联续流二极管;使用专用MOSFET驱动芯片,确保栅极电压稳定。

(3)栅极悬空与干扰

成因:栅极未接偏置或信号源时(悬空),易受外部电磁干扰,积累电荷导致误导通或G-S电压异常升高,最终击穿。

预防措施:未使用的栅极必须接下拉电阻(10-20kΩ)或信号地,高频场景下加RC滤波(如100Ω电阻 + 10nF电容)抑制振荡。

(4)操作不当(焊接、存储等)

成因:

电烙铁未接地或漏电,焊接时瞬间高压击穿栅极;

存储运输中使用非导电包装(如塑料、化纤),积累静电;

引脚频繁弯曲导致内部引线断裂或封装开裂。

预防措施:焊接时使用接地电烙铁,先焊接地引脚;存储运输时使用防静电包装,避免引脚弯曲。

2. 电路设计缺陷

(1)保护措施缺失

成因:未在栅极串联保护电阻(限制瞬态电流)或并联下拉电阻(泄放静电电荷);驱动感性负载时未加续流二极管,导致D-S间反电动势过压。

预防措施:栅极串联保护电阻(10-20kΩ),并联下拉电阻;感性负载并联续流二极管。

(2)偏置与驱动不当

成因:栅极驱动电压不足(低于开启电压VGS(th))或过高(超过最大额定值);高速开关场景中未优化驱动电阻,导致栅极振荡或电压过冲。

预防措施:确保栅极驱动电压在额定范围内(如N-MOS选10-15V驱动),高速开关场景中优化驱动电阻(10-100Ω)。

(3)散热与布局问题

成因:大功率场景下散热设计不足,器件长期工作在高温区(超过结温Tjmax),导致性能退化或热失控;电路布局不合理,栅极走线过长易受干扰,或漏极大电流路径产生电磁耦合。

预防措施:大功率MOSFET配置足够面积的散热片或PCB铜箔;栅极走线尽量短且远离大电流路径,采用屏蔽线或覆地处理。

3. 制造工艺缺陷(批次性失效)

(1)封装与内部结构问题

成因:

固晶层(芯片与基板连接层)分层、厚度不均或固化不良,导致散热失效或机械应力集中,引发接触不良或热敏感失效;

键合引线焊接不牢、氧化或断裂,造成引脚开路;

栅极氧化层厚度不均或存在缺陷,降低ESD耐压能力。

预防措施:严格控制固晶、键合工序参数,定期校准设备;新批次器件抽检ESD耐压和固晶层结合力。

(2)材料与设计缺陷

成因:

保护二极管参数不匹配(如电流容限不足);

芯片掺杂工艺异常,导致沟道导通特性漂移。

预防措施:优化保护二极管设计,严格控制芯片掺杂工艺。

二、针对性对策与预防措施

1. 外部应力防护(操作与环境控制)

(1)静电防护全流程管控

存储运输:使用金属屏蔽袋、导电泡沫或防静电包装,避免接触化纤、塑料。

操作环境:工作台、工具(电烙铁、镊子)可靠接地,操作人员佩戴防静电手环/手套,穿棉质衣物。

电路设计:栅极并联10-20kΩ下拉电阻(泄放感应电荷),高频场景加RC滤波(如100Ω电阻 + 10nF电容)抑制振荡。

(2)过流/过压保护设计

输入保护:可能出现大瞬态电流的回路中串接保护电阻(阻值 R=V surge/I limit ,如限制电流1mA时,R≥1kΩ@1V浪涌)。

耐压设计:选择D-S耐压值(VDS)高于电路最大工作电压1.5倍以上的器件,感性负载并联续流二极管(如肖特基二极管)。

驱动电路:使用专用MOSFET驱动芯片,确保栅极电压稳定在额定范围内(如N-MOS选10-15V驱动)。

(3)规范操作与焊接工艺

焊接时电烙铁断电后利用余热操作,或使用恒温接地焊台(接地电阻<1Ω),先焊接地引脚。

引脚整形时使用防静电镊子,避免过度弯曲(距封装1mm以上操作)。

2. 电路设计优化

(1)栅极驱动与偏置设计

避免栅极悬空,未使用的栅极必须接下拉电阻(10-20kΩ)或信号地。

高速开关场景中,栅极串联阻尼电阻(10-100Ω)抑制振铃,并联TVS二极管(耐压值≤栅极额定电压)吸收瞬态过压。

(2)散热与布局策略

大功率MOSFET配置足够面积的散热片或PCB铜箔,确保结温满足降额要求。

栅极走线尽量短且远离大电流路径,采用屏蔽线或覆地处理;输入输出端并联去耦电容(如100nF),抑制电源纹波干扰。

(3)器件选型原则

优先选择内置保护电阻、ESD防护结构(如VMOS)或集成驱动电路的器件。

大功率场景选栅极电容较大的型号(降低感应电压),小信号场景选高输入阻抗型号。

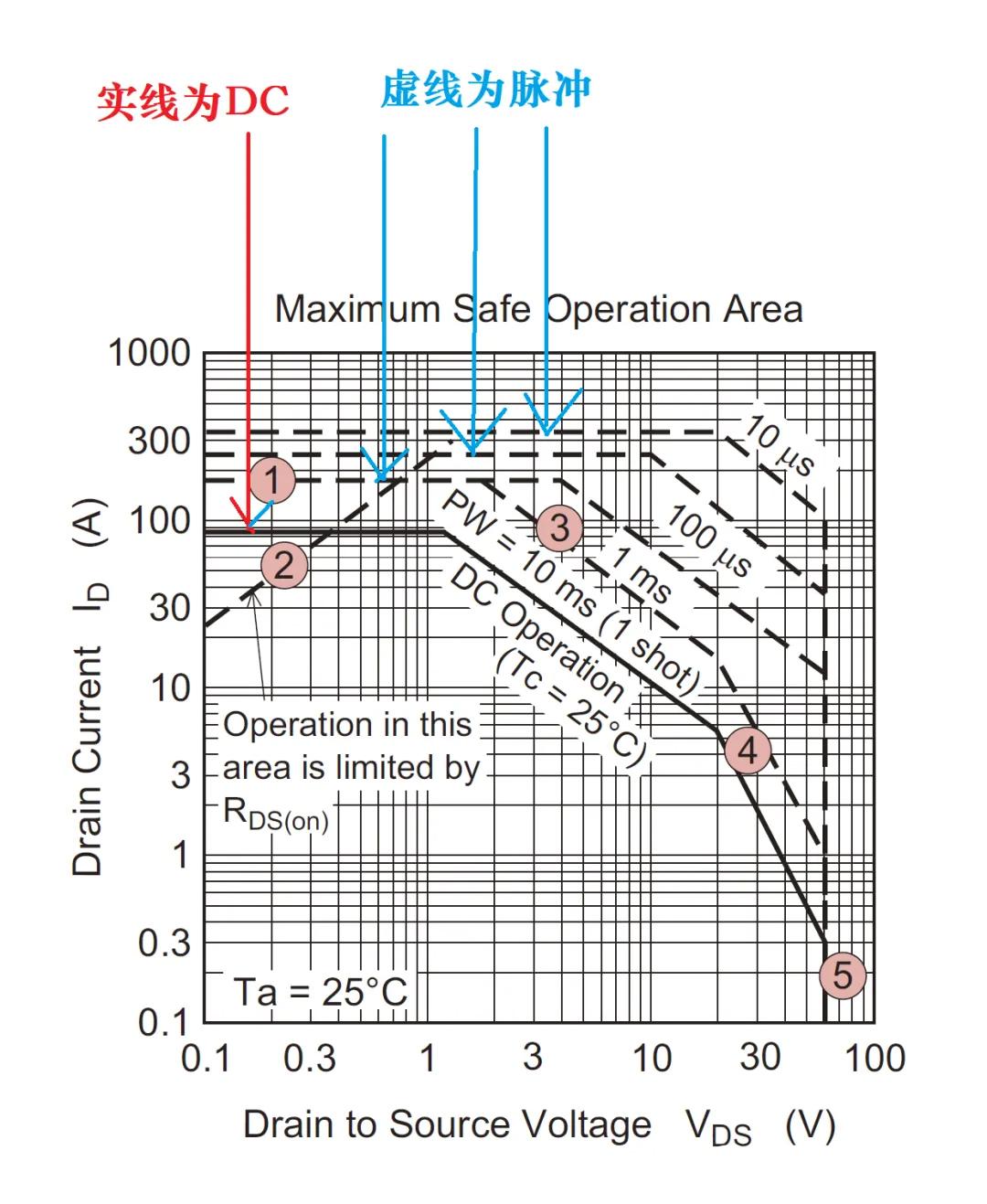

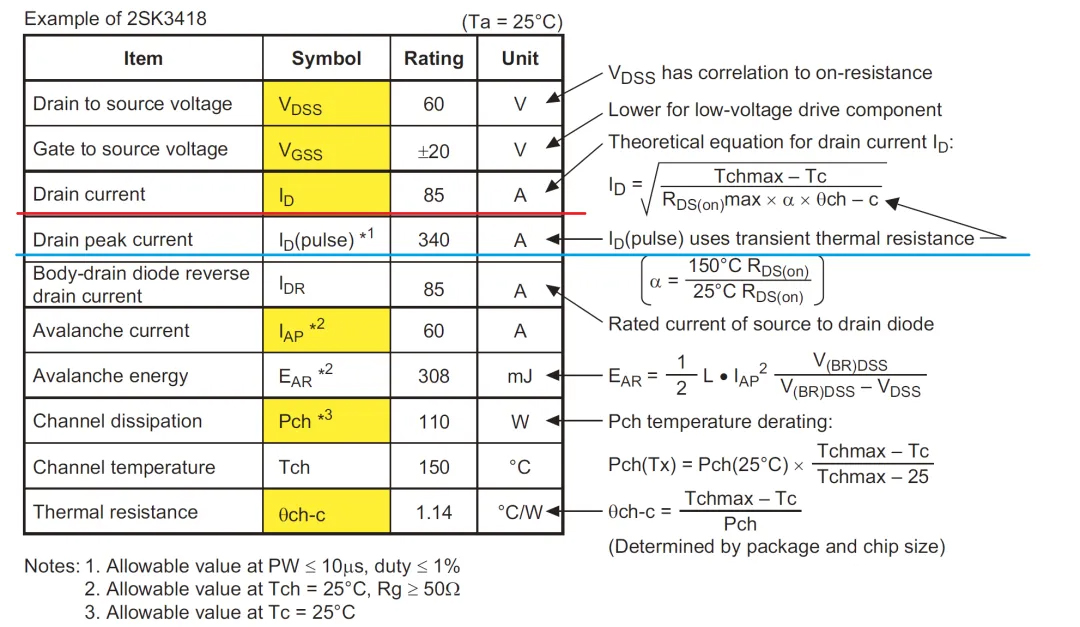

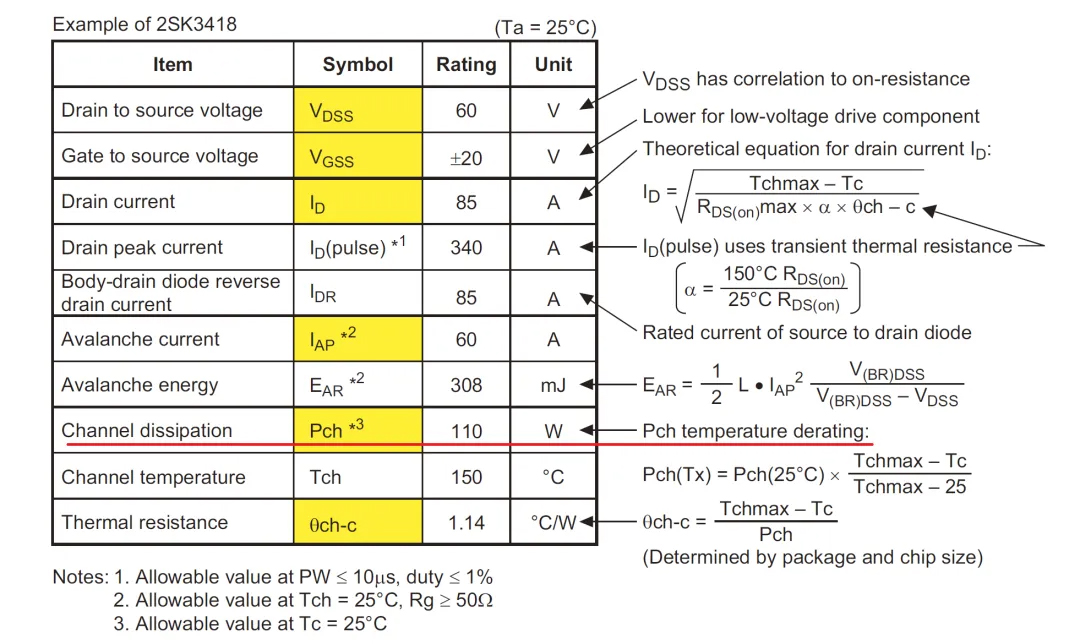

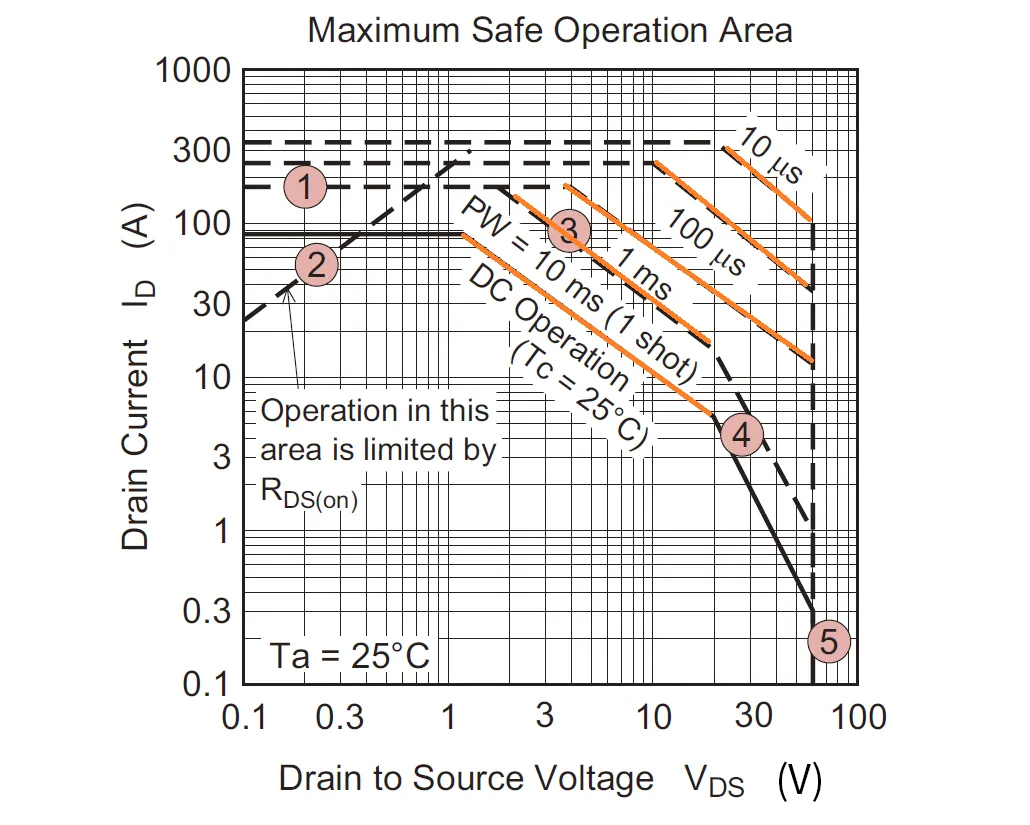

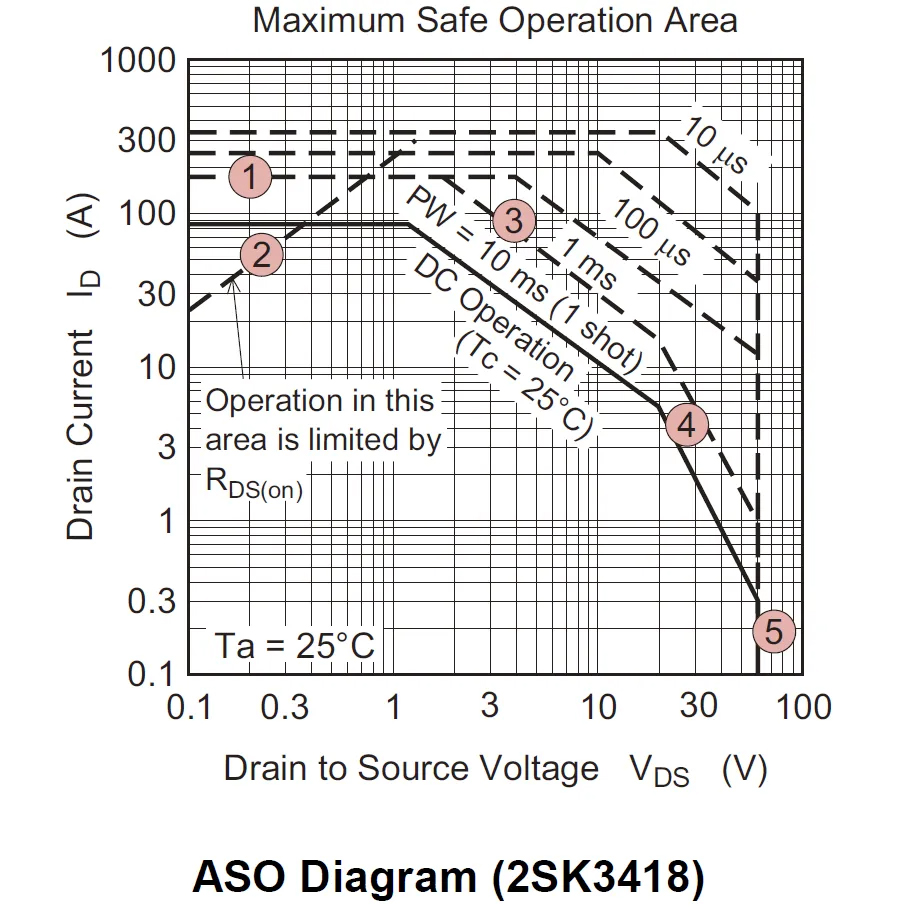

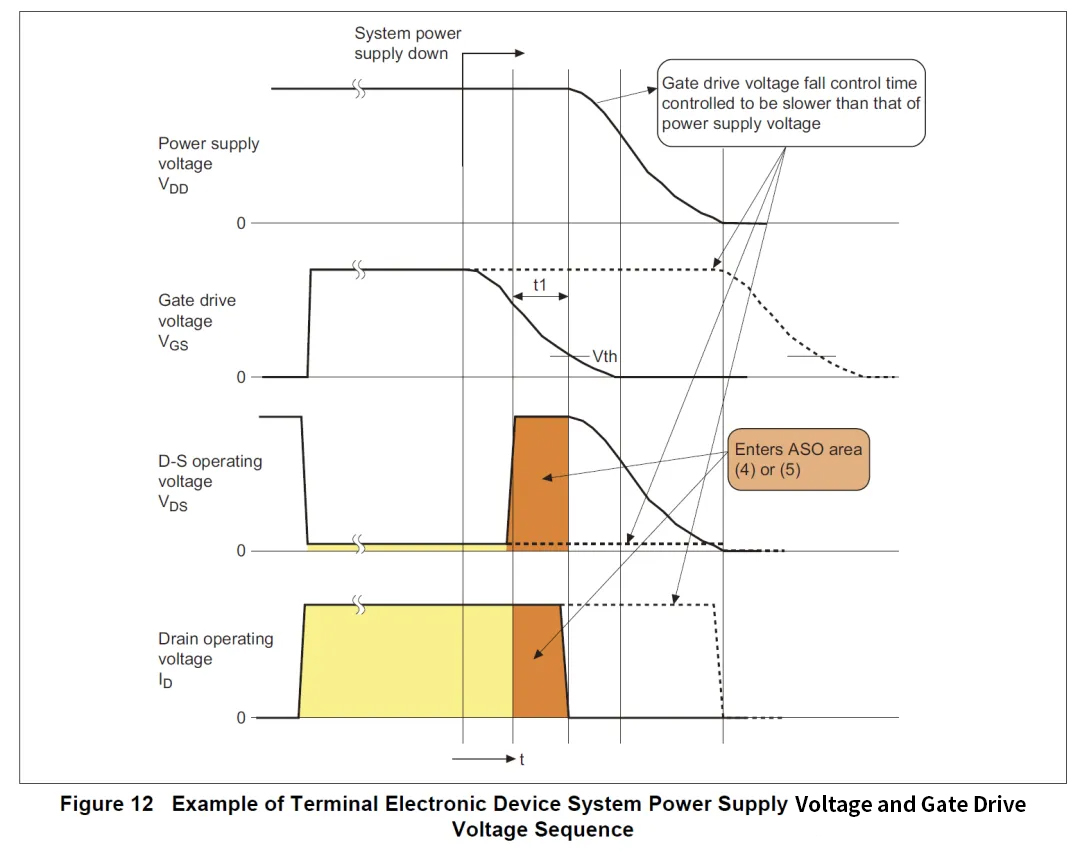

满足电压额定值及降额:漏源电压(VDS)需大于电路中可能出现的最大工作电压(包括瞬态尖峰电压),一般预留20%~30%安全裕量;栅源电压(VGS)需确保驱动电压在安全范围内,避免静电或干扰引入异常电压。

满足电流额定值及降额:连续漏极电流(ID)需大于实际工作电流,同时考虑温升影响;脉冲漏极电流(IDM)需满足短时峰值电流需求,确保不超过器件脉冲额定值。

计算公式:

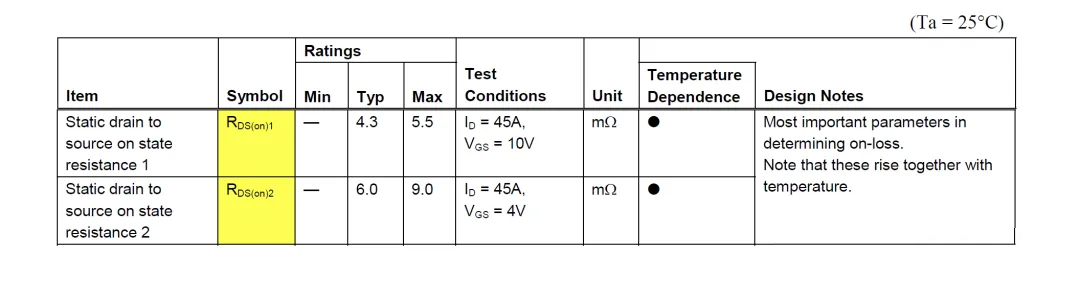

导通电阻(RDS (on))

热性能

3. 制造与质量管控

(1)来料检测与工艺追溯

新批次器件抽检ESD耐压(如±2kV接触放电)、固晶层结合力(拉力测试)。

保留首件样品,失效时对比分析(如C-SAM扫描、SEM成像检查内部结构)。

(2)生产流程优化

固晶、键合工序严格控制参数(如胶水厚度、焊接温度),定期校准设备。

批量生产前进行DFMEA分析,识别潜在失效模式(如热应力、机械应力集中点)。

三、总结

MOSFET失效多源于静电、过流等外部应力与设计、工艺缺陷的叠加作用。通过全流程静电防护(接地、下拉电阻、防静电操作)、电路保护设计(限流电阻、续流二极管)、器件选型优化(内置保护、合适耐压/电流规格)及制造质量管控(来料检测、工艺追溯),可显著降低失效风险。尤其注意:栅极绝不悬空、焊接必须接地、驱动电压合规,是避免人为失效的“黄金三原则”。

深圳市晶扬电子有限公司成立于2006年,是国家重点专精特新“小巨人”科技企业、国家高新技术企业、深圳知名品牌、广东省制造业单项冠军产品、深圳市制造业单项冠军企业,知识产权示范企业,建成广东省ESD静电保护芯片工程技术研究中心,荣获中国发明创业奖金奖等。是多年专业从事IC设计、生产、销售及系统集成的集成电路设计公司,在成都、武汉和加拿大设立有研发中心,拥有超百项知识产权和专利,业内著名的“电路与系统保护专家”。

晶扬电子不仅是深圳静电防护器件的领先者,更是深圳ESD芯片厂家的佼佼者,专注于研发高效、可靠的ESD保护器件,为各类电子产品提供全方位、全覆盖的静电保护、高边开关等保护方案。

主营产品:ESD、TVS、MOS管、DC-DC,LDO系列、工业&车规传感器、高边开关(HSD)芯片、电流传感器、汽车开关输入芯片等。涉及的应用领域有:电脑/笔记本、机顶盒、电视、网络通信、手机、平板、智能穿戴、安防监控、家电、工控、新能源汽车、车载、TWS、电动工具等。

如需产品规格书及领样品请联系

客服电话:19867705160

邮箱:market@jy-electronics.com.cn

官网:www.jy-electronics.com.cn