DC-DC在单板设计中,是数字电路必不可少的部分。工作中遇到过因为DC-DC位置离模拟电路太近,导致模块干扰了音频。DC-DC位置放置在热敏感器件背面,导致因为电感发热损坏了塑料件。还有因为功率电感靠近线缆,传导发射一直超标的问题。

那么如何才能做好一个开关电源的布局?本文主要从3个方面考虑:

1、电源模块放置位置和叠层设计

2、功率器件的布局

3、控制信号的走线

01、电源模块放置位置和叠层设计

在电源模块放置的位置和叠层设计是DC-DC设计的

(1)电源模块尽量考虑负载,减小输出阻抗和线缆对外的辐

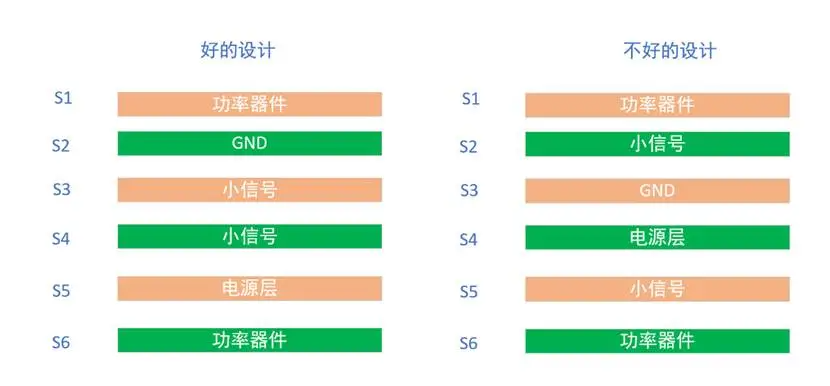

(2)PCB叠层设计

两种设计最主要差别是小信号位置,如果将小信号放在功率层和GND之间,小信号和功率器件之间存在容性噪声耦合。而在推荐的设计中,两个小信号被GND进行了屏蔽。

02、功率器件的布局

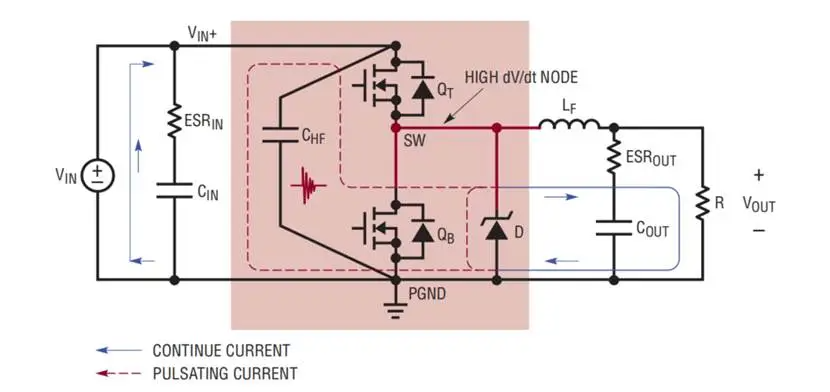

功率器件面积最小化。功率器件回路中存在快速变化的dv/dt和di/dt,面积越大,变化的电场和磁场对外的辐射越强。

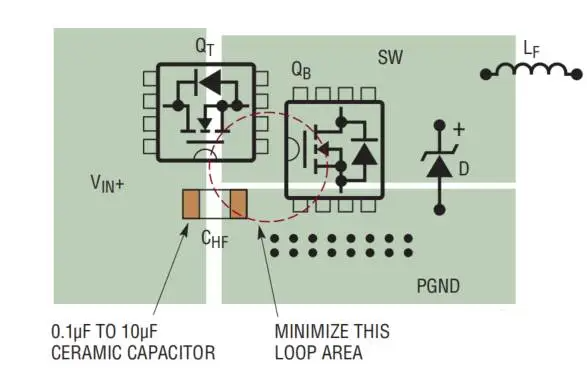

同时,器件焊接后会在PCB板上形成寄生电感,走线越长,寄生电感越大,这些寄生电感在di/dt下,会在MOS管开通和关断的时候形成振铃。振铃会增加器件的损耗,甚至是损耗功率MOSFET。推荐如下布局

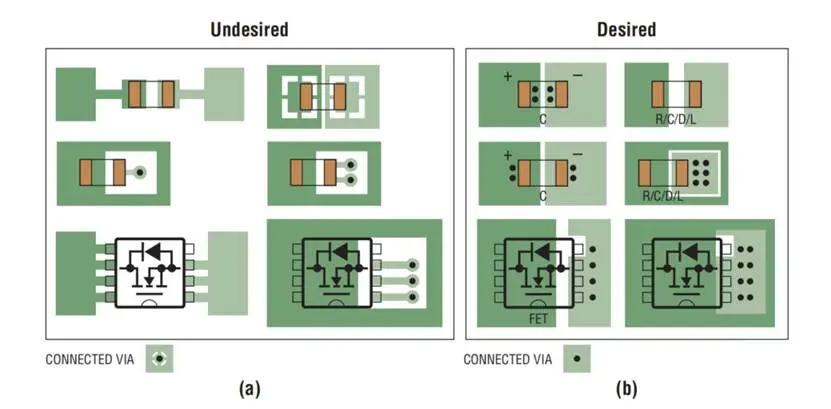

功率器件增加连接点以最小化阻抗。

推荐的设计,能极大的降低PCB寄生电感和器件焊盘与PCB铜箔的阻抗,使得电压降最小化。

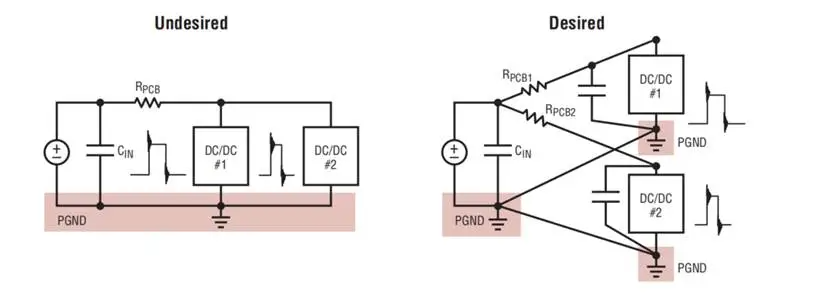

多路电源布局时,输入电流走线需要分开,避免共地干扰。

03、控制电路的布局

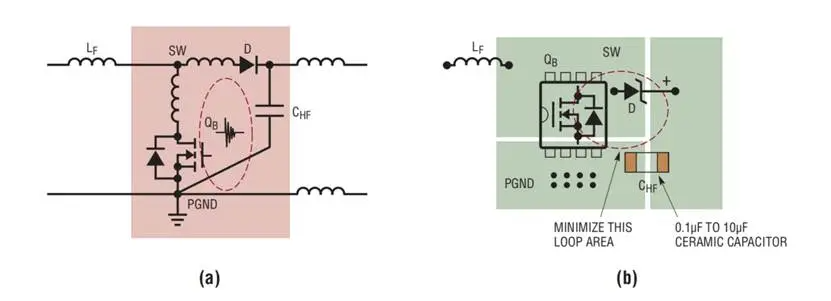

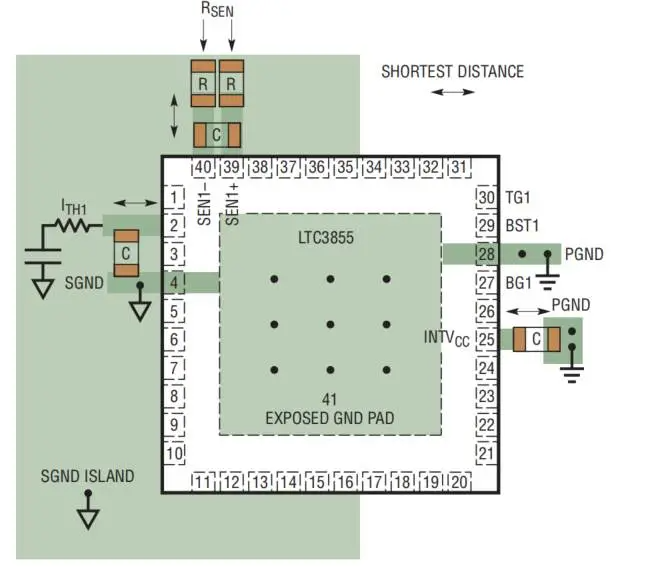

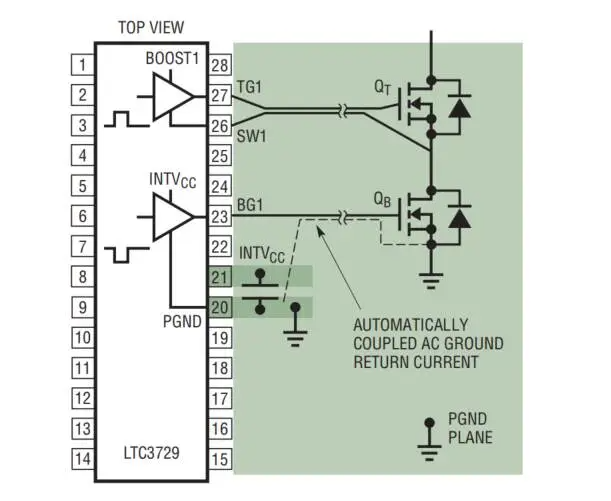

控制电路布局主要有两点:信号地和电源地分离,控制器的去耦电容靠近器件管脚放置。

驱动电路面积尽可能的小,驱动电路走线尽量短。这样做既可以降低阻抗,还能减小在栅极引入的寄生参数。整改过EMC问题的同学应该知道,减小驱动线的长度,不穿层,能极大改善SW处的波形。

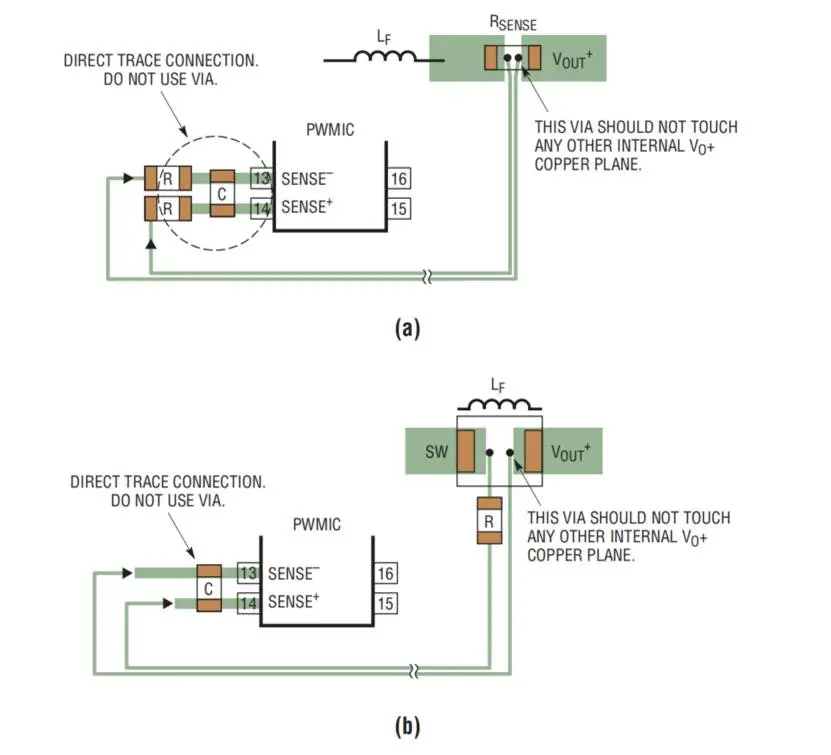

敏感信号采样电阻使用开尔文连接的方式,如果一端是GND,同样要以差分信号的形式走线,降低环路面积和共模干扰。

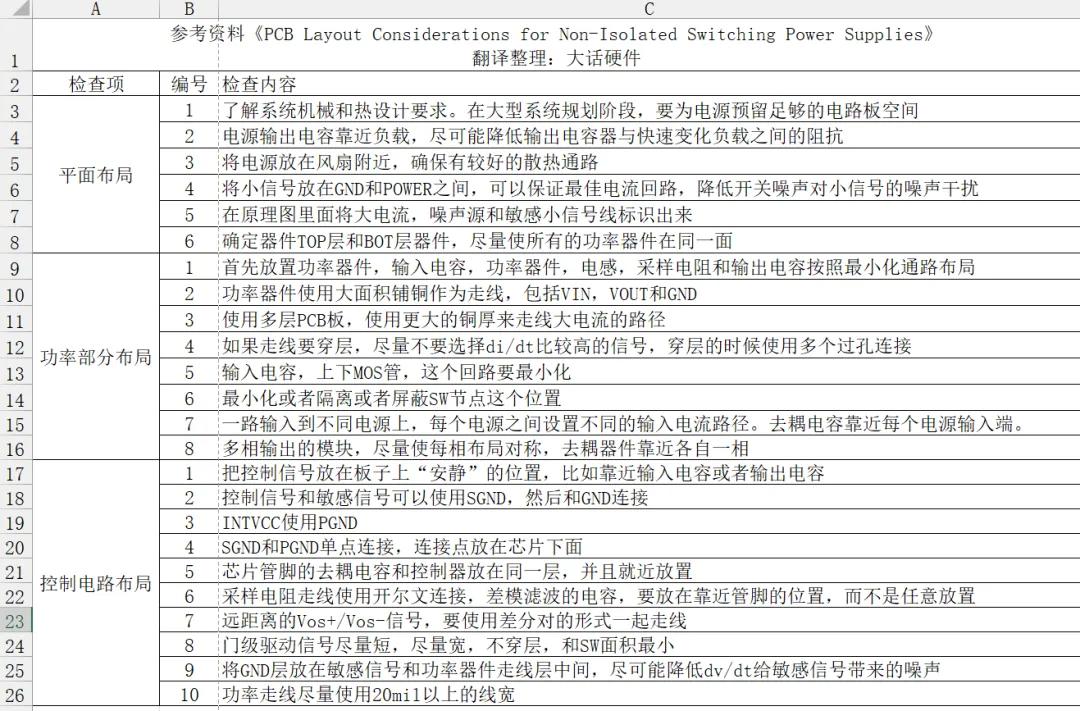

布局要求整理成布局要求如下:

深圳市晶扬电子有限公司成立于2006年,是国家专精特新重点“小巨人”科技企业、国家高新技术企业、深圳知名品牌、广东省制造业单项冠军产品、深圳市制造业单项冠军企业,知识产权示范企业,建成广东省ESD静电保护芯片工程技术研究中心,荣获中国发明创业奖金奖等。是多年专业从事IC设计、生产、销售及系统集成的集成电路设计公司,在成都、武汉和加拿大设立有研发中心,拥有超百项知识产权和专利,业内著名的“电路与系统保护专家”。

晶扬电子不仅是深圳静电防护器件的领先者,更是深圳ESD芯片厂家的佼佼者,专注于研发高效、可靠的ESD保护器件,为各类电子产品提供全方位、全覆盖的静电保护、高边开关等保护方案。

主营产品:ESD、TVS、MOS管、DC-DC,LDO系列、工业&车规传感器、高边开关(HSD)芯片、电流传感器、汽车开关输入芯片等。涉及的应用领域有:电脑/笔记本、机顶盒、电视、网络通信、手机、平板、智能穿戴、安防监控、家电、工控、新能源汽车、车载、TWS、电动工具等。

如需产品规格书及领样品请联系

客服电话:19867705160

邮箱:market@jy-electronics.com.cn

官网:www.jy-electronics.com.cn